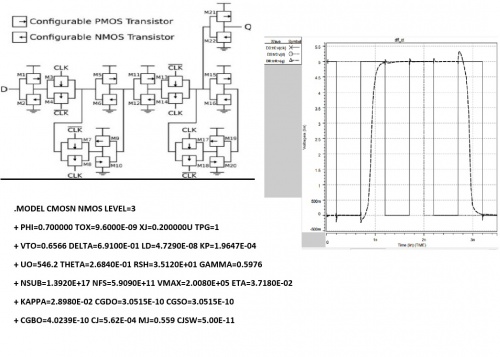

شبیه سازی فلیپ فلاپ نوع D با ترانزیستورهای قابل پیکربندی در HSPIC

این فایل zip شامل پروژه ای با عنوان شبیه سازی فلیپ فلاپ نوع D با ترانزیستورهای قابل پیکربندی در HSPIC میباشد. مدار فلیپ فلاپ نوع D با ترانزیستورهای قابل پیکربندی از مقاله ای با عنوان Fighting stochastic variability in a D-type flip-flop with transistor-level reconfiguration انتخاب شده و در HSPIC شبیه سازی شده است. به همراه توضیح فارسی نتیجه ی شبیه سازی. مناسب برای درس الکترونیک دیجیتال پیشرفته و دروس مشابه. قسمتی از کد HSPIC: ********************************************************M22-nmos M221 q n6 0 0 CMOSN L=1U W=5U M222 q n6 0 0 CMOSN L=1U W=10U M223 q n6 0 0 CMOSN L=1U W=20U M224 q n6 0 0 CMOSN L=1U W=30U M225 q n6 0 0 CMOSN L=1U W=50U M226 q n6 0 0 CMOSN L=1U W=80U M227 q n6 0 0 CMOSN L=1U W=100U *************************************************print .TEMP 25 .TRAN 1p 10N .PRINT TRAN V(d) V(clk) V(clkb) V(q) .OPTIONS LIST NODE POST ***************************************************************************nmos model .MODEL CMOSN NMOS LEVEL=3 + PHI=0.70 …